## Fault-latch circuit protects switchers

Craig Varga, National Semiconductor, Phoenix, AZ

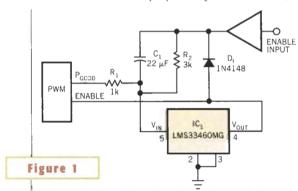

ANY POWER-SUPPLY designers like to have a regulator latch off in the event of an overcurrent situation or other fault condition. Yet, many PWM controllers do not internally support this latch-off function. Most do, however, have a power-good output and an enable function. The circuit in Figure 1 adds that latch-off capability at low cost in little additional space. The design is based on the LMS33460, which is a power-supply monitor in a tiny, five-lead SC-70 package. You just need to combine it with a few small passive parts, and the circuit is complete. When the Enable Input signal goes high, the voltage at the top of C, rises quickly to 5V. Because the output voltage is not yet alive,  $P_{GOOD}$  stays low, charging C, through R<sub>1</sub>. Because the voltage on C<sub>1</sub> is zero at the instant of turn-on, Pin 5 of IC, pulls up to 5V and begins to drop at a time constant that C<sub>1</sub>, R<sub>2</sub>, and R<sub>3</sub> determine. If the output does not reach its normal operating voltage before the Pin 5 voltage drops to less than 3V, IC, pulls its output low and latches the regulator off.

If, however, the output comes into regulation before the latch times out, P<sub>GOOD</sub> goes high and C<sub>1</sub> begins to discharge, raising the voltage on Pin 5 and keeping the supply enabled. R, provides a couple of volts to IC, to keep the IC alive in the event of a latch condition, and D, pulls down on the PWM's Enable when the system-enable command switches low. C, can be a small tantalum or ceramic capacitor. If you use a ceramic unit, choose a good dielectric, such as X5R. Also, the 5V supply's rising in less than 1 msec or so may eliminate the Enable, and

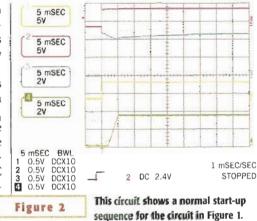

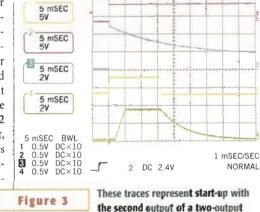

the whole circuit simply runs from the 5V supply. Figure 2 shows a normal start. and Figure 3 shows start-up with the second output of a twooutput regulator shorted. In both cases, the top trace is regulator shorted. the system-enable

signal, the second trace is IC,'s Pin 5, the third trace is the PWM Enable at IC,'s Pin 4, and the bottom trace is the

regulator's output voltage. You can see in Figure 3 that IC,'s Pin 5 decays to 3V, at which point it pulls the PWM Enable low, latching off the regulator.

This circuit adds a latch-off function to PWM controllers lacking this feature.